Программа проверки строчных команд процессорного ядра

Краткое описание программного обеспечения

Программа предназначена для проверки строчных команд 16-разрядного процессорного ядра, совместимого по архитектуре и системе команд с микроконтроллером Intel 80186.

Проверка работоспособности строчных команд процессорного ядра осуществляется с помощью последовательного выполнения следующих тестов:

– Тест проверки строчной команды lods.

– Тест проверки строчной команды stos.

– Тест проверки строчной команды scas.

– Тест проверки строчной команды movs.

– Тест проверки строчной команды cmps.

Программа загружается в оперативную память FPGA-реализации микроконтроллера через последовательный интерфейс UART и запускается на исполнение. Обеспечивает проверку работоспособности строчных команд процессорного ядра lods, stos, scas, movs, cmps.

Функциональные характеристики программного обеспечения

Проверка работоспособности строчных команд процессорного ядра осуществляется с помощью последовательного выполнения следующих тестов:

– Тест проверки строчной команды lods.

– Тест проверки строчной команды stos.

– Тест проверки строчной команды scas.

– Тест проверки строчной команды movs.

– Тест проверки строчной команды cmps.

Тест проверки строчной команды lods.

Проверка строчной команды lods производится в следующем порядке. Предварительно в сегмент памяти размером 65536 байт записывается последовательность констант, построенных по заданному алгоритму. Затем производится чтение последовательности записанных констант с помощью строчной команды lods и сравнение прочитанных констант с эталонными значениями, которые также формируются по аналогичному алгоритму. Поскольку команда lods обеспечивает чтение данных и в байтовом и в словном форматах, то проверка команды производится в два этапа. Сначала производится проверка команды lodsb, затем производится проверка команды lodsw. Тест считается успешно завершённым, если все данные, считанные из сегмента ОЗУ с помощью строчной команда lods, совпали с эталонными значениями.

Тест проверки строчной команды stos.

Проверка строчной команды stos производится в следующем порядке. Предварительно эталонная константа заносится в регистр AX. Затем эта константа с помощью строчной команды rep stos записывается в сегмент памяти размером 65536 байт. После этого производится проверка содержимого сегмента памяти на соответствие записанным данным. Поскольку команда stos обеспечивает запись данных и в байтовом и в словном форматах, то проверка команды производится в два этапа. Сначала производится проверка команды stosb, затем производится проверка команды stosw. Тест считается успешно завершённым, если все данные, записанные в сегмент ОЗУ с помощью строчной команда stos, совпали с эталонными значениями.

Тест проверки строчной команды scas.

Проверка строчной команды scas производится в следующем порядке. Предварительно во все ячейки сегмента ОЗУ размером 65536 байт записывается эталонная константа. Затем эта эталонная константа заносится в регистр AX. После чего с помощью строчной команды rep scas проверяется содержимое сегмента ОЗУ на соответствие эталонной константе, размещённой в регистре AX. Поскольку команда scas обеспечивает сканирование данных и в байтовом и в словном форматах, то проверка команды производится в два этапа. Сначала производится проверка команды scasb, затем производится проверка команды scasw. Тест считается успешно завершённым, если все данные, записанные в сегмент ОЗУ, при сканировании строчной командой scas совпали с эталонным значением, размещённым в регистре AX.

Тест проверки строчной команды movs.

Проверка строчной команды movs производится в следующем порядке. Предварительно в сегмент ОЗУ размером 65536 байт записывается последовательность констант, построенных по заданному алгоритму. Затем производится пересылка содержимого этого сегмента ОЗУ в другой не использованный сегмент ОЗУ размером 65536 байт с помощью строчной команды rep movs. После этого производится сравнение содержимого исходного сегмента ОЗУ и сегмента, заполненного с помощью команды rep movs. Поскольку команда movs обеспечивает пересылку данных и в байтовом и в словном форматах, то проверка команды производится в два этапа. Сначала производится проверка команды movsb, затем производится проверка команды movsw. Тест считается успешно завершённым, если все данные, размещённые в исходном сегменте, при сравнении совпали с данными, перемещёнными во второй сегмент с помощью строчной команда rep movs.

Тест проверки строчной команды cmps.

Проверка строчной команды cmps производится в следующем порядке. Предварительно в два разных сегмента ОЗУ размером 65536 байт каждый записывается последовательность констант, построенных по заданному алгоритму. Затем производится сравнение содержимого этих сегментов с помощью строчной команды rep cmps. Поскольку команда cmps обеспечивает сравнение данных и в байтовом и в словном форматах, то проверка команды производится в два этапа. Сначала производится проверка команды cmpsb, затем производится проверка команды cmpsw. Тест считается успешно завершённым, если при сравнении содержимого двух сегментов ОЗУ с одинаковыми данными строчная команда rep cmps не обнаружила ошибок.

Перечень технических средств и программного обеспечения, необходимого для установки и эксплуатации программного обеспечения

Для установки и эксплуатации программы проверки строчных команд процессорного ядра необходимо следующее оборудование и программное обеспечение:

1. Персональный компьютер, с установленной операционной системой Windows 7.

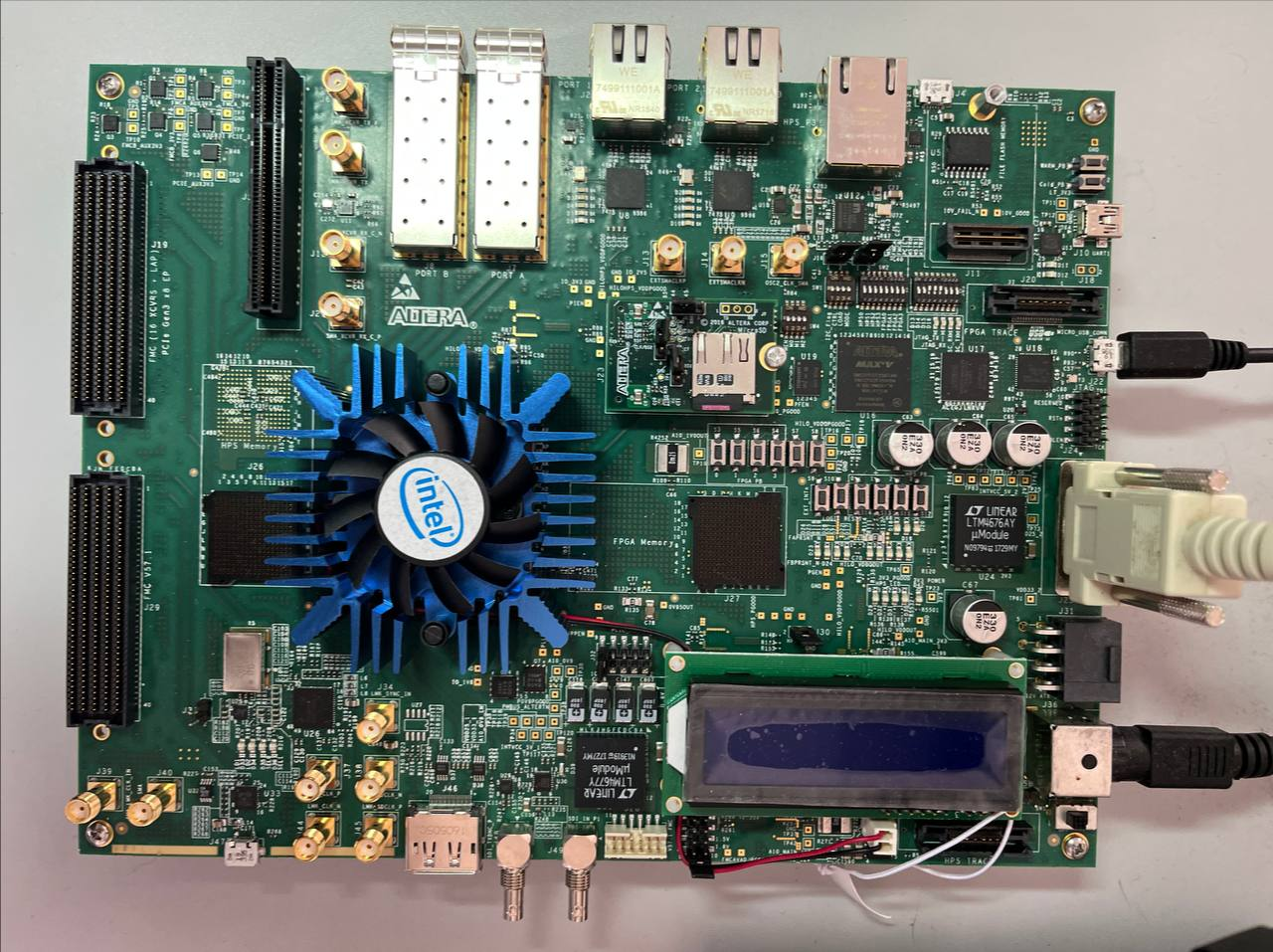

2. Отладочная плата на базе FPGA Arria 10 фирмы Altera с источником питания (Рисунок 1).

Рисунок 1

3. Интерфейсный блок, необходимый для подключения отладочной платы к COM- порту персонального компьютера.

4. Образ СнК SSV16, загружаемый в FPGA, в виде файла SSV16.sof. СнК SSV16 представляет собой систему на кристалле, построенную на основе 16-разрядного процессорного ядра, совместимого по архитектуре и системе команд с микропроцессором Inlel 80186. В состав СнК SSV16 входит ряд периферийных блоков, включая блок процессорного ядра.

5. Стандартная программа Quartus II, необходимая для загрузки файла SSV16.sof в FPGA.

6. Программа Монитор (Monitor186.exe), необходимая для загрузки Программы проверки строчных команд процессорного ядра в отладочную плату и отображения результатов проверки блока. Программа Монитор входит в состав поставки программы проверки строчных команд процессорного ядра.

7. Исполняемый модуль программы проверки строчных команд процессорного ядра TestCPU.exe.

Инструкция по установке программного обеспечения

1. Подключить интерфейсный блок отладочной платы на базе FPGA к COM-порту персонального компьютера с операционной системой Windows.

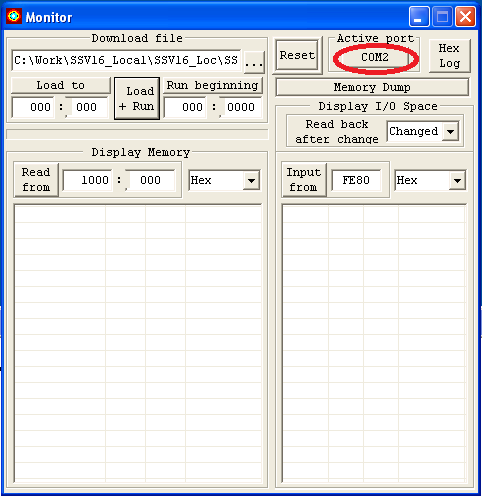

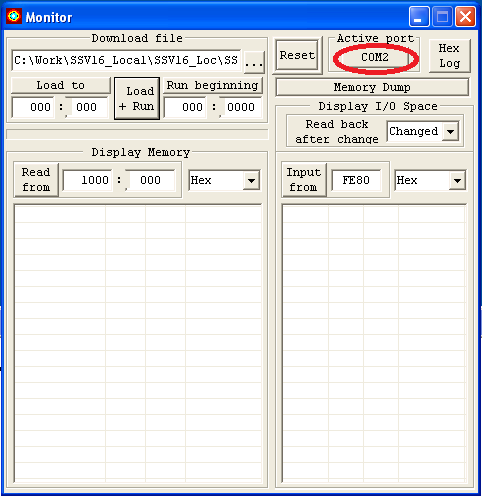

2. Запустить на компьютере технологическую программу Монитор (Monitor186.exe). С помощью меню программы выбрать номер COM-порта, через который к компьютеру подключается отладочная плата и установить скорость и режимы работы COM-порта (рисунок 2).

3. Включить питание отладочной платы на базе FPGA.

4. С помощью стандартной программы Quartus II загрузить в FPGA отладочной платы файл SSV16.sof, содержащий в своём составе образ СнК SSV16. После завершения загрузки файла SSV16.sof в отладочном окне программы Monitor186 должен появиться символ «*». Появление символа «*» в отладочном окне программы Monitor186 свидетельствует о готовности начального загрузчика СнК SSV16 к приёму и отработке команд программы Monitor186.

Рисунок 2

Инструкция по эксплуатации программного обеспечения

1. В поле Download file программы Monitor186 выбрать программу проверки строчных команд процессорного ядра (TestCPU.exe) в каталоге рабочей папки, с помощью кнопки Load + Run программы Monitor186 загрузить её в ОЗУ СнК SSV16 и запустить на выполнение (рисунок 3).